AMD Zen 3 EPYC “Genesis” A0 sample specs leak – Due to release this year

AMD Zen 3 EPYC “Genesis” A0 sample specs leak – Due to release this year

What Igors’ Lab has confirmed is what we have already come to expect; that Zen 3 will not bring higher core counts to AMD’s EPYC product line. With Zen 3 continuing to use 7nm transistors, the architecture offers customers both performance benefits through design and lithography refinements, not more cores and colossal transistor evolutions.

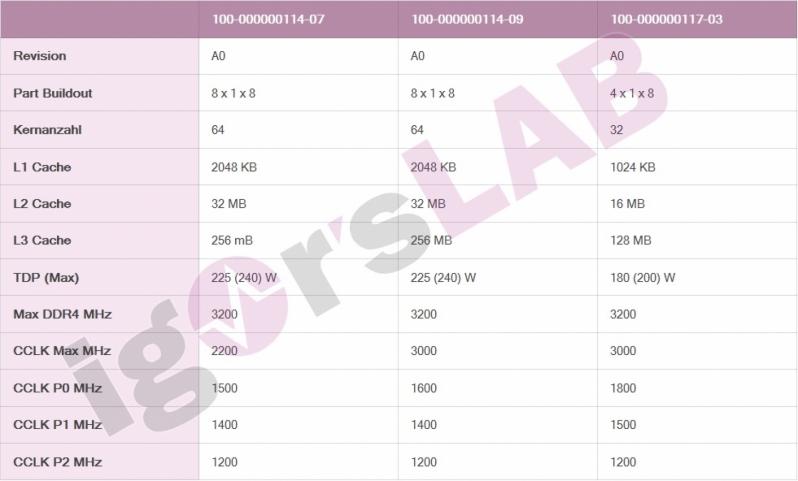

Below we can see that AMD’s 3rd generation of EPYC processors will continue to max out at 64 cores and 256MB of L3 cache, revealing no major changes over their Zen 2 counterparts. That said design changes and clock speed alterations should be enough to ensure that Zen 3 delivers more performance than Zen 2 across a wide range of workloads. Â

It is also noting that these processors are said to be early A0 samples, which means that AMD’s release-ready Zen 3 processors will likely boast higher core clock speeds than what is shown below. Â

As we have detailed several times before, starting in early October 2019, AMD’s Zen 3 series of processors will feature several significant design changes that go beyond merely adding more cores and threads into the mix. Â

While multi-threaded performance is important, single-threaded performance and lower internal latencies also matter, especially in day-to-day consumer workloads and gaming scenarios. This area is where AMD’s Zen 3 cores will be focused.Â

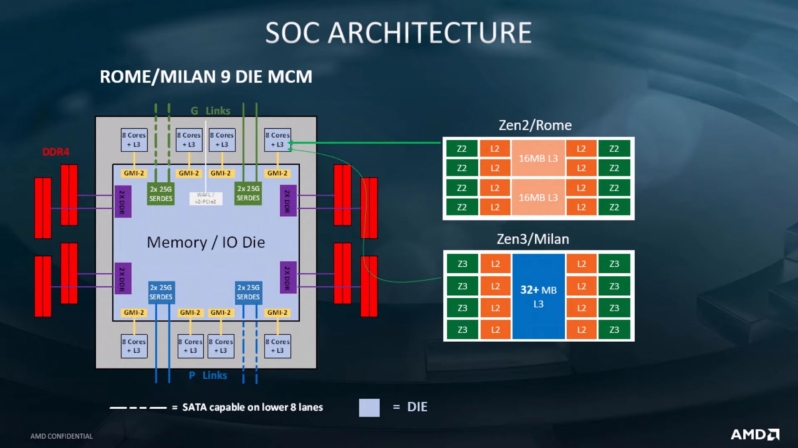

In the slide below, we can see that AMD is offering users a “combined cache” within each of their eight-core Zen 3 chiplets. This means that AMD’s L3 cache will be equally shared across all cores within a Zen 3 CCX, instead of being split between four cores each. This design shift will help AMD to lower its internal latencies within a Zen 3 CPU die, allowing individual cores to communicate faster and for individual cores to be able to access any data on each chip’s L3 cache without major latency bumps. This, amongst other things, will help Zen 3 to deliver higher performance levels in latency-limited workloads.Â

With AMD’s Milan silicon entering its A0 state, the company can no longer make major changes to Zen 3’s design, at least architecturally. Now, AMD will be focused on testing its Zen 3 processor designs, finding the clock speeds that their new processors can achieve in real-world use cases. This testing will allow AMD to define the full specifications of its retail processors, which will define how powerful Zen 3 processors will be when they release later this year.Â

You can join the discussion on AMD’s Zen 3 EPUC “Genesis” processors on the OC3D Forums.Â