Early Zen 5 Turin leak suggests large IPC increase for AMD’s next-gen CPUs

Early Zen 5 “Turin” benchmark showcases impressive Cinebench R23 results

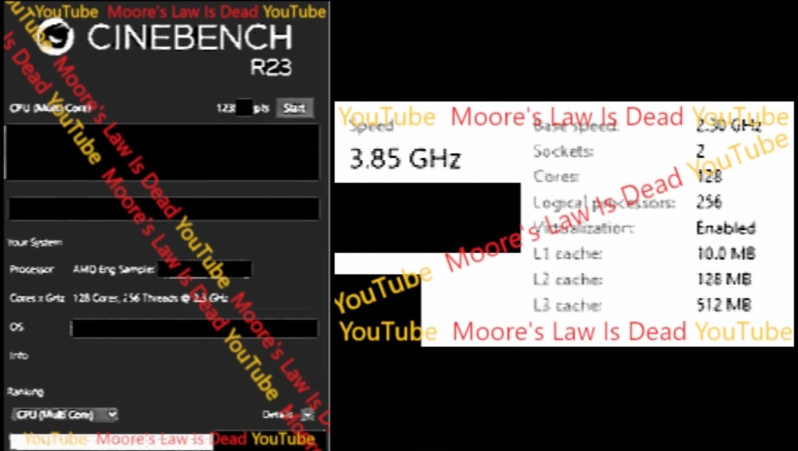

Moore’s Law is Dead has leaked a new Cinebench R23 score for an alleged Dual 64-core Zen 5 “Turin” based system, revealing new architectural details about AMD’s Zen 5 CPU architecture and impressive performance numbers from AMD’s early Zen 5 silicon.Â

With a Cinebench R23 score of over 123,000, AMD’s dual-Turin powered 128-core 256-thread system was able to deliver 15% more performance than a the fastest Zen 4 Genoa system on HWBOT’s benchmarking database. This is with early Zen 5 silicon and with a processor that had a lower listed base clock than the compared Genoa Zen 4 system, though it is unknown what clock speeds the Zen 5 CPUs ran at during the benchmark.

It is likely that AMD will be able to improve the clock speeds of their Zen 5 Turin processors before they launch next year, with Moore’s Law is Dead suggesting that AMD will deliver 20+% IPC gains over Zen 4 with their Zen 5 processors and slightly higher core clock speeds. If AMD can achieve these kinds of performance gains, Zen 5 will place the company in a very strong position in 2024.

With today’s Zen 5 leak, it looks like AMD’s upcoming Zen 5 processors will feature an enlarged L1 cache and the same L2 and L3 cache sizes as their Zen 4 predecessors. Zen 5 CCDs will have eight CPU cores (with Zen 5 Dense coming with 16 cores), 80KB of L1 Cache per core, 1MB of L2 Cache per core, and 32MB of L3 Cache per CCD (without V-Cache). Zen 4 processors have 64MB of L1 cache per core, giving Zen 5 CPUs 25% more L1 cache per core.

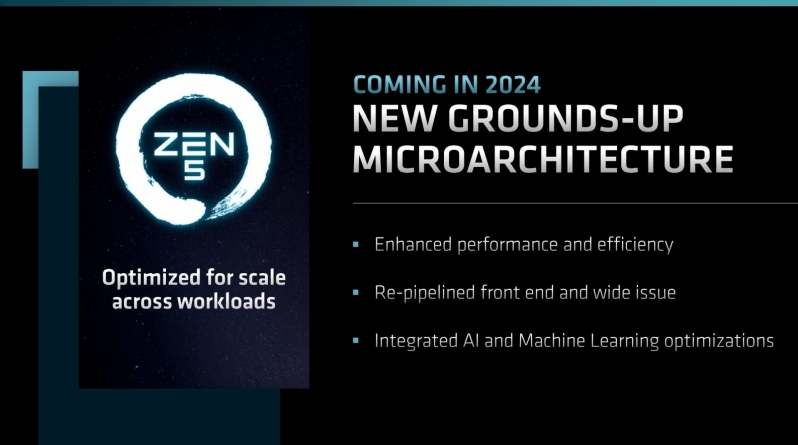

AMD’s Zen 4 processors are due to launch in 2024, with Moore’s Law is Dead suggesting an early 2023 launch timeframe. With Zen 4, AMD will be focusing on enhancing the performance and efficiency of their processors, promising a “re-pipelined front-end and wide issue” alongside “integrated AI and machine learning optimisations”.

One of AMD’s focuses with Zen 4 was on increasing core clock speeds, and with Zen 5 AMD will be focusing heavily on IPC and efficiency gains. With Zen 4, AMD redesigned their cores to make them run at higher clock rates, and with Zen 5 AMD will be optimising those core designs to get more work out of every clock cycle and to integrate features that will enhance AMD’s performance in more niche workloads. Â

You can join the discussion on AMD’s leaked Zen 4 Turin CPU benchmark on the OC3D Forums.