New instructions and more performance – Intel reveals AVX10, AVX10.2, and APX

Intel aims to deliver more performance with future CPUs using AVX10, AVX10.2, and new APX instructions

There are three main ways to boost the performance of CPUs. First there are clock speed increases, boosting the number of clock cycles (work) that can be done in any given time. Next there are core/architectural changes, which can allow more work to be completed during each clock cycle. And finally is the addition of new CPU instructions, which add new capabilities to processors to accelerate workloads.

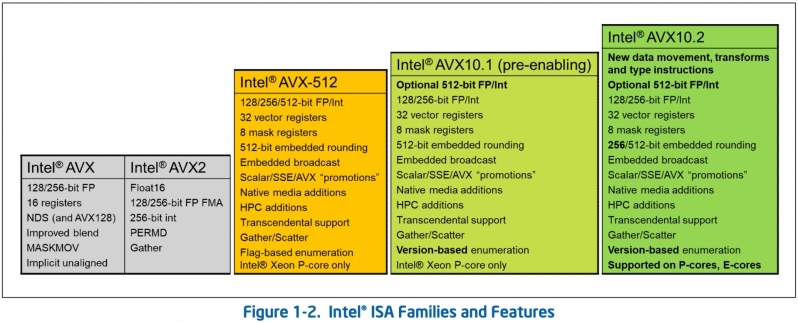

Today, Intel has made a trio of announcements, revealing AVX10, AVX 10.2, and Intel APX. Ultimately, these new changes are how Intel are going to maintain AVX-512 functionality and extend the capabilities of their processors moving forward. This is also how Intel plans to deliver instruction set parity between their P-core and E-core CPU designs, with AVX-512 being P-core only.

Intel Advanced Performance Extensions (Intel APX)

With the addition of new instructions, Intel wants to enhance the performance of their processors, allowing tasks to be completed with fewer CPU resources, allowing CPUs to do more work, or do the same work with lower power draw.Â

With Intel APX, Intel are doubling the number of general purpose registers (GPRs) from 16 to 32, allowing compilers to keep more values in registers and increase overall CPU performance with APX-compiled code. This should enable notable power savings and performance gains, with the good news for developers being that these changes should not require code changes, all it will need is a new compiler.Â

Intel APX doubles the number of general-purpose registers (GPRs) from 16 to 32. This allows the compiler to keep more values ??in registers; as a result, APX-compiled code contains 10% fewer loads and more than 20% fewer stores than the same code compiled for an Intel® 64 baseline.2 Register accesses are not only faster, but they also consume significantly less dynamic power than complex load and store operations.

Intel APX should first arrive on new Intel processors sometime in the latter half of 2024, and will likely be available in all new Intel processors starting in 2025.

Developers should be able to benefit from APX by simply recompiling their software with a new APX compatible compiler, enabling notable performance gains with minimal effort. With the introduction of Intel’s Granite Rapids processors, APX instructions will be made available to Intel’s enterprise customers.

AVX10 – The future of AVX-512

Intel’s AVX-512 instruction set has a strange history, with support for these instructions being available in some processor generations and not others. Oddly Intel’s 12th Generation and 13th generation Core processors don’t support AVX-512, despite the fact that their 11th generation counterparts did. This is due to the hybrid nature of Intel’s latest CPUs, as Intel’s P-Core designs support AVX-512, but their E-Core designs do not. Since Intel’s latest CPUs have a mix of these cores, not all CPU cores support AVX-512 instructions and the processors therefore cannot support AVX-512.

Today, Intel’s AVX-512 instructions are only supported on their P-Core only Xeon processor designs, limiting the number of workloads that can benefit from AVX-512 instructions. With AVX10, Intel are moving on from AVX-512, making the feature available exclusively in P-Core only designs as an optional/legacy feature.

Instead of adding AVX-512 support to their E-cores, Intel are creating AVX10.2 to unify the capabilities of their P-Core and E-Core designs, bringing more capabilities to Intel’s latest E-core and P-core designs, without adding unnecessary features to their space-optimise E-cores.

AVX10 and AVX10.2

Intel will start delivering AVX10 support with their Xeon processors, with AVX10.1 acting as a stepping stone before AVX10.2 support arrives on future Intel processors.

AVX10.1 will be Xeon P-core only and will add new features to Intel’s processors, with AVX10.2 arriving to deliver unified instruction set supports between both P-core and E-core products. AVX10.2 will be supported by P-Core only designs, E-core only designs, and hybrid P-core and E-core CPU designs.Â

With AVX10, support for 512-bit will be optional. Intel will only offer AVX512 ISA support on their P-core designs as a legacy support option, and E-cores will not support AVX-512. In effect, Intel’s AVX-512 instruction set has been frozen, and Intel will no longer be adding new capabilities to AVX-512. In a sense, Intel are abandoning AVX-512.

AVX10 is Intel’s way of moving on from AVX-512 and its complex history. Moving forward, Intel will be adding new instructions to their processors and leave AVX-512 support as a legacy option for users of their P-Core only processor designs. This means that we should not expect a return of AVX-512 to Intel’s consumer-grade hybrid CPU designs, but we can expect to see new capabilities come to Intel’s hybrid CPUs thanks to AVX 10.2.Â

You can join the discussion on Intel AVX10, AVX10.2, and APX on the OC3D Forums.