SK Hynix reveals its 8th Generation 300-layer 3D NAND, promising lower costs and higher performance levels

SK Hynix’s new 300-layer NAND chips promise increased performance and bit density

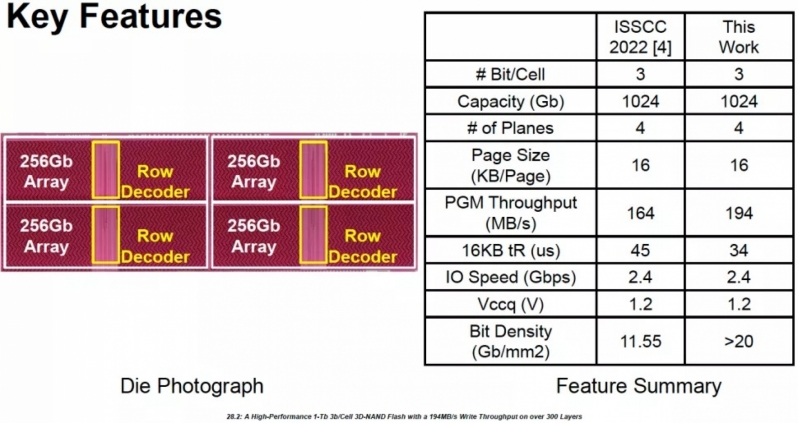

At the ISSCC 2023 conference, SK Hynix has revealed their 8th generation 3D NAND technology. While the company kept a lot of information about this NAND to themselves, they confirmed that their new NAND features over 300 active layers, and that this new NAND will enable SK Hynix to increase the performance of future SSDs and offer customers lower per-TB NAND prices.

SK Hynix’s initial 8th Gen 300+ layer NAND chips will be available with 1Tb (128GB) capacities with TLC (3 bits per cell) NAND cells. These chips will offer users bit densities of 20Gb/mm2Â and offer users a maximum throughput of 194 MB/s, which is 18% higher than the company’s 7th Generation 238-layer NAND.

With their latest NAND chips offering users a near 20% increase in maximum throughput, we can be sure that high-performance SSD manufacturers will transition to this newer NAND to deliver fast I/O speeds. This will be especially true for manufacturers who want to create the fastest PCIe 5.0 SSDs.Â

At this time, it is unknown when SK Hynix’s 8th generation 3D NAND will hit the market, though it is likely to arrive in late 2024 or 2025. At this time, SK Hynix’s 8th Generation NAND is only at its prototype development stage. Â

The technological improvements which will be included with SK Hynix’s 8th Generation NAND include the following.Â

– Triple-Verify Program (TPGM) feature that narrows cell threshold voltage distribution and reduces tPROG (program time) by 10%, which translates into higher performance

– Adaptive Unselected String Pre-Charge (AUSP) – another procedure to reduce tPROG by around 2%

– All-Pass Rising (APR) scheme that reduces tR (read time) by approximately 2% and cuts word line rising time

– Programmed Dummy String (PDS) technique that cuts world line settling time for tPROG and tR by reducing channel capacitance load

– Plane-Level Read Retry (PLRR) capability that allows to change read level of a plane without terminating others therefore issuing subsequent read commands immediately and improving quality of service (QoS) and therefore read performance

You can join the discussion on SK Hynix’s 8th Generation 300+ layer 3D NAND on the OC3D Forums.Â